Over the past few weeks, I've decided that there are a two things I don't like about the current 2065 emulator. These are:

- In the real 2065, several things would happen at once every 10 ns sub-cycle. The software emulator is necessarily much more sequential;

- The blinkenlights console doesn't get updated frequently enough.

Rather radically, I have therefore decided to change the emulator from a software emulator into a hardware emulator. Inspired by Lawrence Wilkinson's model 30 emulator on an FPGA, I'm going to implement the 2065 emulator on an FPGA as well.

The idea is to have the 2065 CPU and memory, as well as the logic to control the console panel on the FPGA board. For now, I'm not going to implement channel I/O on the FPGA, in stead, the FPGA will be interfaced with a PC running a software emulator of the channel and other I/O hardware.

The interface between the FPGA and the sioftware I/O will need to be able to support the following actions:

- The FPGA tells the software to execute an IPL, START I/O, TEST I/O, HALT I/O or TEST CHANNEL command;

- The software has read and write access to main memory implemented on the FPGA board;

- The software signals interrupt status to the FPGA board;

- The FPGA board signals interrupt completion to the FPGA board.

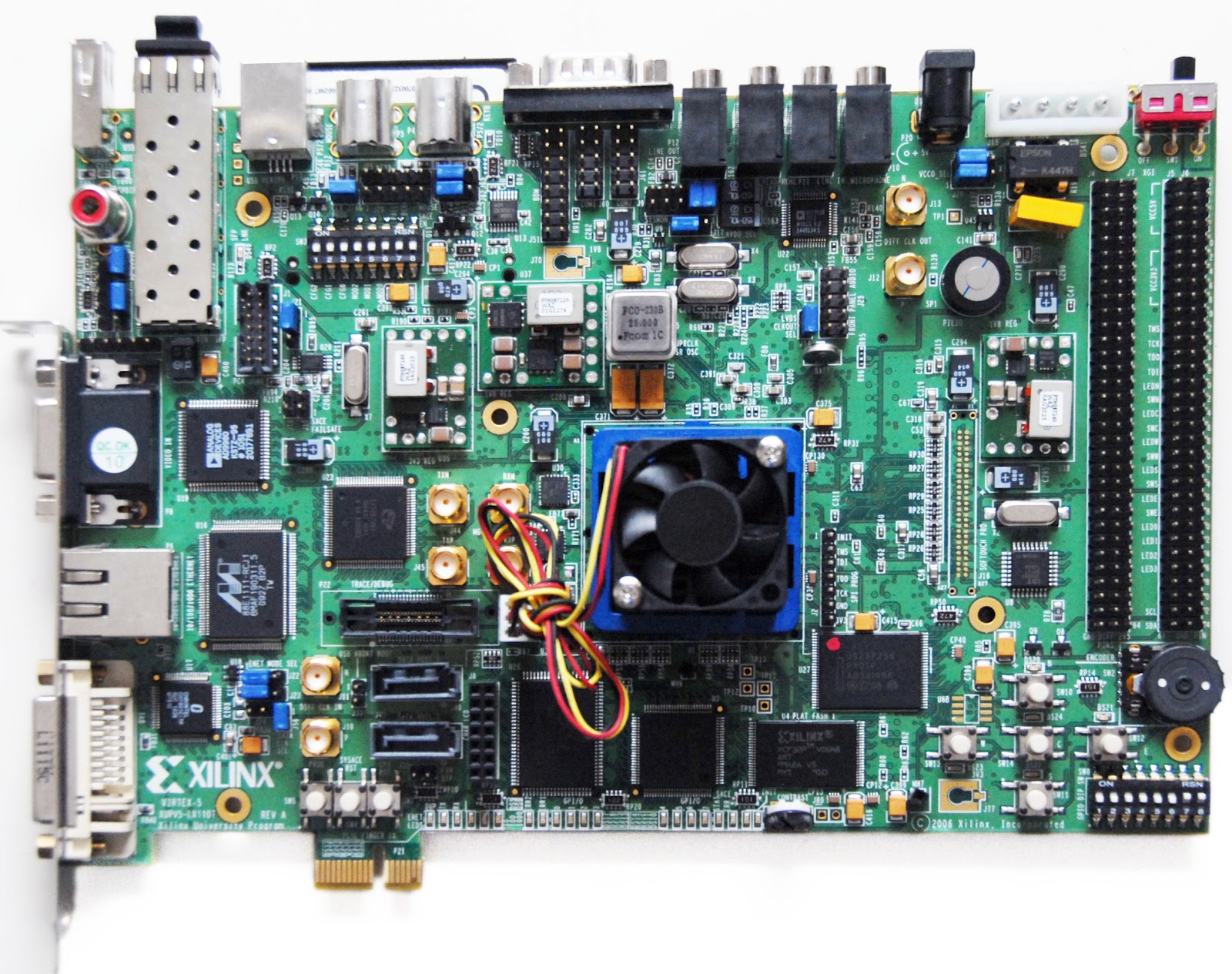

The interface needs to be reasonably fast and reliable. I found that FPGA development boards are available that fit into a PCIe slot. I've selected the Xilinx XUPV5 board pictured above for this project, as it has ample logic, a PCIe interface, and I/O pins that don't use exotic connectors.

Next thing to do is to build a small interface to connect the XUPV5 to the shift registers that drive the console panel.