### CHAPTER 2

#### INSTALLATION

PDOS can be configured for a host of different system configurations. These range from small, TMS9995 based STD modules to the 128K byte, TMS9900 based TM990/102 CPU module. This chapter begins by walking a new user through a typical boot procedure. Specific hardware modules are then described including jumper and cabling instructions. Finally, a SYSGEN procedure is described along with trouble shooting ideas.

| 2.1 HARDWARE CONFIGURATIONS2-3               |

|----------------------------------------------|

| 2.2 GETTING STARTED2-4                       |

| 2.2.1 SYSTEM BOOT2-4<br>2.2.2 BOOT EPROMS2-9 |

| 2.3 PDOS SUPPORTED HARDWARE2-12              |

| 2.3.1 CPU2-12                                |

| 2.3.1.1 SBC 95/1 CPU                         |

| 2.3.1.2 TM990/101MA CPU                      |

| 2.3.1.3 TM990/102 CPU2-15                    |

| 2.3.2 MEMORY2-17                             |

| 2.3.2.1 ER3232 32K STATIC RAM2-17            |

| 2.3.2.2 MATRIX 7911/RPC 32K STATIC RAM2-18   |

| 2.3.2.3 TM990/201 STATIC RAM2-19             |

| 2.3.2.4 TM990/203A DYNAMIC RAM2-20           |

| 2.3.3 SECONDARY STORAGE2-21                  |

| 2.3.3.1 ER3300 FLOPPY CONTROLLER2-21         |

| 2.3.3.2 ER3314 WINCHESTER INTERFACE2-22      |

| 2.3.3.3 GW3 FDC/1 FLOPPY CONTROLLER2-25      |

| 2.3.3.4 TM990/210 BUBBLE MEMORY2-26          |

| 2.3.3.5 TM990/303A FLOPPY CONTROLLER2-27     |

| 2.3.4 SPECIAL PURPOSE2-29                    |

| 2.3.4.1 ER3318 GRAPHICS2-29                  |

| 2.3.4.2 TM990/302 EPROM PROGRAMMING2-31      |

| 2.3.4.3 TM990/307 I/O EXTENDER2-32           |

| 2.3.5 CARD CAGE2-33                          |

PDOS 2.4 DOCUMENTATION

### (CHAPTER 2 INSTALLATION continued)

| 2.4 | YSGEN2-                                      | ·34 |

|-----|----------------------------------------------|-----|

|     | 2.4.1 DISK FORMATTING2-                      | -34 |

|     | 2.4.2 DISK INITIALIZING2-                    | 35  |

|     | 2.4.3 CUSTOMIZING PDOS2-                     | 36  |

|     | 2.4.4 DISK BACKUP2-                          | 39  |

| 2.5 | YSTEM ADDRESSING2-                           | 40  |

|     | 2.5.1 CRU ADDRESS ASSIGNMENTS2-              | 41  |

|     | 2.5.2 MEMORY MAPPED I/O ASSIGNMENTS2-        | 43  |

|     | 2.5.3 PDOS MEMORY CONSTANTS2-                | 45  |

|     | 2.5.4 INTERRUPT AND XOP VECTOR DEFINITIONS2- | 47  |

| 2.6 | ROUBLE SHOOTING2-                            | 48  |

PAGE 2-2

PAGE 2-3

### 2.1 HARDWARE CONFIGURATIONS

The following table is intended to give a cross reference of available support hardware different CPU's. These have been tested and are known to work under the PDOS operating system.

|         |                         | CPU    |      |         |

|---------|-------------------------|--------|------|---------|

|         |                         | /101MA | /102 | SBC95/1 |

| MEMORY  |                         |        |      |         |

|         | ER3232                  | x      |      |         |

|         | TM990/201-206           | X      |      |         |

|         | TM990/203A              | X      | х    |         |

|         | MATRIX 7911/RPC         |        |      | ×       |

| STORAGE |                         |        |      |         |

|         | TM990/303A              | x      | x    |         |

|         | ER3314                  | x      | х    |         |

|         | TM990/210               | х      | х    |         |

|         | ER3300                  | x      |      |         |

|         | GH3 FDC/1               |        |      | х       |

|         | MICRO/SYS SASI          |        |      | x       |

| SPECIAL |                         |        |      |         |

|         | THOOD (202 CDDON DUDNED | v      |      |         |

Typical system configurations:

| 1-TM990/101MA | 9900 CPU, 64K byte SRAM      |

|---------------|------------------------------|

| 2-ER3232      | 4 ports, floppy storage      |

| 1-TM990/303A  | 4 cards, 3 amps              |

|               |                              |

| 1-TM990/101MA | 9900 CPU, 64K byte DRAM      |

| 1-TM990/203A  | 2 ports, floppy storage      |

| 1-TH990/303A  | 3 cards, 4 amps              |

|               |                              |

| 1-TM990/101MA | 9900 CPU, 128K byte SRAM     |

| 4-ER3232      | 6 ports, floppy & winchester |

| 1-ER3314      | 6 cards, 10 amps             |

|               |                              |

| 1-TM990/102   | 9900 CPU, 128K byte DRAM     |

| 1-TH990/307   | 5 ports, floppy storage      |

| 1-TM990/303A  | 3 cards, 4 amps              |

|               |                              |

| 1-SBC 95/1    | 9995 CPU, 64K byte SRAM      |

| 2-Matrix RAM  | 2 ports, floppy & winchester |

| 1-GW3 FDC/1   | 5 cards, 2 amps              |

| 1-M/S SASI    |                              |

| TM990/302 EPROM BURNER | Х |   |

|------------------------|---|---|

| TM990/306 SPEECH       | X | X |

| TM990/307 I/0          | Х | Х |

| ER3318 GRAPHICS        | x | X |

# 2.2 GETTING STARTED

Although there are many different PDOS system contigurations, only one is shown here. Changes from one contiguration to another are mainly limited to different controllers and CPU switch settings. (The TM990/102 does not have CPU switches and hence the boot menu prompts for installed devices.)

Shown here is a system consisting of a TM990/101MA CPU card, a TM990/303A floppy controller, and any combination of RAM cards such that memory is contiguous from >0000 to a minimum of >8000 and a maximum of >E000. The boot workspace is at >7000. Terminals should be configured for 1 start bit, 7 bit character, even parity, and 2 stop bits.

You must follow each step carefully for a correct system boot. Do not proceed to the next step without successfully completing the previous step.

#### 2.2.1 SYSTEM BOOT

STEP 1 VERIFY BOOT PROGRAM.

\*\*Do not insert PDOS disk until Step 4.

- [] Verify correct voltages on empty card cage.

- [ ] Install PDOS boot EPROMs on CPU card.

- [] Verify all CPU jumpers.

- [] Turn OFF (open) all switches on CPU card.

- [] Install CPU and RAM only in card cage.

- [] Connect terminal to main port.

- [] Power up system.

- [] Ground RESTART.B momentarily (pin 93 on card cage) and hit (carriage return).

\*\*Do not proceed until PDOS menu comes up. Error messages 'DTR LOW' and 'CHECKSUM ERROR' should be resolved before continuing.

Typical system configuration:

TM990/101MA (32K bytes RAM) TM990/303A 2-SA800 TM990/510

9900 CPU RAM from >1000 to >8000+ Floppy controller Floppy drives Card cage

9902 initialized for 11 bits: 1 start bit 7 bit character

- 1 even parity

- 2 stop bits

\*POOS BOOT R2.4 0-99=800T 100=MEMORY TEST 101=IAC 102=BOOT 103=MAKE BOOT 104=AUX ?\_

#### CHAPTER 2 INSTALLATION

PAGE 2-5

(2.2.1 SYSTEM BOOT continued)

### STEP 2 VERIFY SYSTEM MEMORY.

[] Run memory test by entering '100<carriage return>'.

\*\*Do not proceed until memory verifies. Each successful pass of memory is indicated by a period. Memory errors are reported as the memory address followed by the exclusive 'OR' of the read and write data. ?100.....?

?101

0 10

0000: 2FDC 2306 2F7C 02FA 2F7C 02FA 2FDC ...

0010: 2F7C 0644 2F7C 0644 2F7C 0644 2F7C ...

10

0010: 2F7C

0012: 2F7C

0012: 0644^C

STEP 3 VERIFY STATIC DISK CONTROLLER OPERATION.

- [] Turn off power.

- [] Enable CPU controller switch (switch #2 on).

- [] Install one mass storage controller (e.g. 303A).

- [] Connect drives to controller verifying correct cabling.

- [] Power up system and drives.

- [ ] Ground RESTART.B and hit <carriage return>.

- [] Verify correct controller self test (if any).

\*\*Do not insert PDOS disk at this time!

\*\*Do not proceed until PDOS menu again comes up.

STEP 4 VERIFY DISK READ OPERATION BY BOOTING SYSTEM.

- [ ] Verify that PDOS boot disk is write protected.

- [] Power up system and drives. NEVER power up or down the system with a diskette in drive and door closed!

- [ ] Ground RESTART.B and hit <carriage return>.

- [ ] Insert PDOS boot disk in drive and close door.

- [] Enter disk number followed by <CR>.

- [] Verify drive selects and R/W head loads.

- [] Wait for 'BOOTED!' reply.

- [] Hit (carriage return).

- [] Verify PDOS banner and that the LED on the CPU card is blinking on and off at 1 second intervals.

Auto Boot /\_\_\_\_ Units 0-3 = 303A Floppy // Units 4-7 = 3314 Winchester ///\_\_\_\_ Units 8-11 = 210 Bubble ////\_\_\_\_ Units 12-99 = 3300 Floppy 11111 P4 ///// P3 P2 .-----!/////!-----XXXXXXXX--XXXXXXX--. 11111 0 ! 11111 S12345 1 1145 TM990/101MA U44 1143 U42 1

P1

0-99=800T 100=MEMORY TEST 101=IAC 102=800T 103=MAKE B00T 104=AUX ?0 800TED! PD0S/101 R2.4 ERII, COPYRIGHT 1982 DATE=MN,DY,YR \_

\*PDOS BOOT R2.4

PAGE 2-6

#### (2.2.1 SYSTEM BOOT continued)

\*\*If the system seems to hang and returns error 102 (>0066) after an extended period, then:

- 1. Verify controller jumpers.

- 2. Verify by ohming out drive cabling.

- 3. Verify correct drive termination.

- 4. Verify BUS grant signals on card cage.

\*\*If any other errors are reported, a disk alignment problem would be indicated. Verify with drive distributor that disk drives are correctly aligned.

\*\*If LED is blinking but the PDOS prompt does not appear, verify that DTR (pin 20) signal at CPU main port is high. (This condition is indicated by the message 'DTR LOW' before the boot menu.)

STEP 5 VERIFY CORRECT PDOS BOOT.

- [] Enter DATE and TIME. Spaces or commas may be used as delimiters. Seconds are optional. All line entries end with (carriage return).

- [] Enter 'CS'. A period should be the only response.

- [] Enter 'LT'. Verify the 'BM' is >6000 and 'EM' is the end of the system memory.

- [] Enter 'LS'. The disk directory should list to console.

\*\*If the system returns an error 80 to the 'CS' command, then the boot was not correctly read. The boot itself may have been altered. Verify correct memory configuration again and then consult your distributor.

You have now correctly booted the PDOS system. Only steps 4 and 5 need be repeated to boot a system after a system has been checked out. If this is an initial system boot, continue on with steps 6 through 9 to backup your system disk and configure PDOS for your specific terminal.

PD0S/101 R2.4 ERII, COPYRIGHT 1982 DATE=MN, DY, YR 7 14 82 TIME=HR, MN, SC 10 1 .CS .LT TASK PAGE TIME HS PC ... TB \*0/0 O з >6020 >619A >0828 ... .LS DISK=PDOS R2.4 LEV NAME:EXT TYPE SIZE ... 8/8 ... 1 ALOAD SY ASM 1 SY 52/52 ... BACKUP 6/6 ... 1 SY 1 BFIX SY 11/11 ...

#### CHAPTER 2 INSTALLATION

PAGE 2-7

(2.2.1 SYSTEM BOOT continued)

STEP 6 FORMAT A NEW DISKETTE.

- [] Verify boot disk is in drive 0.

- [] Place new disk in drive 1.

- [] Enter 'FRMTxxx', where 'xxx' is device type.

- [] When format header displays, open the door on drive O.

- [] Proceed with formatting disk in drive 1. Enter 'LOGICAL DISK UNIT=' as 1. Enter 'TRACKS=' as <carriage return>. Enter 'FORMAT LOGICAL DEVICE 1?' with 'Y'.

**\*\***If formatting is not successful, verify hardware configuration and then repeat STEP 6 with another new disk. (Always use good quality, double density diskettes.)

STEP 7 BACKUP SYSTEM DISK.

- [] Close door on disk drive 0.

- [] Enter 'BACKUP'.

- [] Backup disk in disk drive 0 (source disk) to disk in disk drive 1 (destination disk). Verify the correct number of sectors. Enter (carriage return) for 'DISK NAME'.

STEP 8 CONFIGURE PDOS SYSTEM.

- [] Enter 'BFIX'.

- [] Select system terminal type.

- [] Answer all 'ADJUST' questions with <CR>'s.

- [] Answer 'DISK #=' with 1 to fix a new boot on disk device 1.

- [ ] Remove boot disk from drive 0 and store in a safe, dry, cool place.

\*\*If your terminal type is not listed, then refer to section 2.4.3 CUSTOMIZING PDOS for instructions on how to define your own control code sequences.

STEP 9 [] Place new backed up boot disk in drive 0. [] Reboot system (steps 4 and 5).

FRMT303 TM990/303A STANDARD FLOPPY FORMAT R2.4 LOGICAL DISK DEVICE=1 SIDES=1 TRACK=0,76 FORMAT LOGICAL DEVICE 1, SECTORS 0 TO 76?Y

SUCCESS!!

.BACKUP DISK BACKUP R2.4 SOURCE DISK=0 DESTINATION DISK=1 NUMBER OF SECTORS=1976 READY?Y DUPLICATE 'PDOS 2.4'?Y FINISHED SECTOR 100 SUCCESS! BACKUP DISK NAME= RENAMED 'PDOS 2.4' .BFIX BOOT FIX R2.4 \*\*CAUTION: EXECUTE ONLY AFTER NEW BOOT! TERMINALS: A=ADDS REGENT 25 D=DECSCOPE (VT52 or VT100) H=HAZELTINE 1520 I=INTERTUBE II L=LEAR SEIGLER S=SOROC U=USER DEFINED TYPE=S ADJUST TIMER EVENTS (Y OR N)? ADJUST SYSTEM CLOCK (Y OR N)? ADJUST CONSOLE CRU BASE ADDRESSES (Y OR N)? CHANGE SYSTEM INTERRUPT MASK (Y OR N)? AUTO-START UPON BOOT (Y OR N)? ADJUST AUTO-START FILE NAME (Y OR N)? ADJUST INITIAL MEMORY LIMIT (Y OR N)? ADJUST PDOS PROMPT (Y OR N)? DISK #=1 BOOT SECTOR=1846 CONTINUE?Y BOOT SUCCESSFULLY WRITTEN

PDOS 2.4 DOCUMENTATION

### CHAPTER 2 INSTALLATION

(2.2.1 SYSTEM BOOT continued)

#### FLOPPY DISK MAINTENANCE

Safety precautions should always be followed with respect to the treatment of diskettes.

- 1. Never power up or down a system with a diskette in the drive and the door closed. Only after power has been turned on and a RESET or RESTART activated, should the drive door be closed.

- Protect diskettes by always storing them in protective jackets when not in use.

- 3. Do not touch the media with your fingers. Do not bend or fold the diskette.

- 4. Store your diskettes in a cool, dry place. Preferably, the temperature and humidity should be constant and the same as where they are used. Never expose the diskettes to the sun or extreme temperatures.

- 5. Carefully load and unload the diskettes from the drives. Avoid bending.

- Do not expose the diskettes to strong magnetic fields. (e.g. terminal transformers, power supplies, magnets, etc.)

Power up procedure

Store diskettes in jackets

Do not touch media

Environment

Loading and unloading

Magnetic fields

PAGE 2-8

------

PIER Z INSTALLATION

#### 2.2.2 BOOT EPROMS

The PDOS boot EPROMs contain read and write logical sector routines and a system boot program. Entry addresses are at address >F800 and include controller initialization and motor off routines. Other functions include memory inspect/change and test programs.

The read and write sector routines are the link between PDDS and a secondary storage device. Reference to a 256 byte sector is by disk number (R0), logical sector number (R1), and buffer address (R2). Errors are returned in register R0. They are device dependent and range from 100 to 32768.

Memory addresses >F000 through >FFFF are reserved for EPROM routines. The boot EPROMs reside at memory addresses >F800 through >FFFF. The entry points are located at address >F800 and are defined as follows:

- >F800 READ LOGICAL SECTOR. XRSE and XRSZ

primitives pass R0, R1, and R2 to this

routine. (See 5.2.11 READ SECTOR.)

- >F804 WRITE LOGICAL SECTOR. XWSE passes R0, R1, and R2 to this routine. (See 5.2.23 WRITE SECTOR.)

- >F808 INITIALIZE LOGICAL SECTOR. XISE passes R0, R1, and R2 to this routine. Initialize sector is equivalent to write sector except that no PDOS ID check is made on the header sector. (See 5.2.7 INIT SECTOR.)

>F80C INITIALIZE CONTROLLER. This routine is called once via a 'BL' instruction before PDOS system initialization. Device dependent initialization procedures are handled here.

>F810 MOTOR OFF ROUTINE. This routine is called once every second via a 'BL' instruction and is for controller devices, which need constant attention. Such is the case with 5" mini-floppies, which require the motor to be turned off after a period of inactivity. Read and write logical sector System boot Memory inspect and change Memory test

RO=disk # R1=logical sector R2=buffer address

|       | AORG >F800      |                      |

|-------|-----------------|----------------------|

| BOOTV | B <b>axrsez</b> | ;READ SECTOR         |

|       | B OXWSEZ        | ;HRITE SECTOR        |

|       | B ƏXISEZ        | ;INITIALIZE SECTOR   |

|       | B AXDITC        | ;INIT CONTROLLER     |

|       | RT              | ;MOTOR OFF (IGNORED) |

CHAPTER 2 INSTALLATION

PAGE 2-10

(2.2.2 BOOT EPROMS continued)

The bootstrap program begins executing via the LOAD vector at memory address >FFFC. If auto-boot has been selected (generally through a CPU switch), then the program proceeds to boot the system from the lowest installed disk device. Otherwise, the program waits for a character on the main CPU port.

The first character entered is timed and used to set the baud rate of the main console port. This is referred to as auto-bauding a port. A carriage return auto-bauds all ports correctly.

After the port has been bauded, the boot program sums memory from >F800 to >FFFA. If this sum is nonzero, then a 'CHECKSUM ERROR' message is reported indicating that something has happened to the EPROMs and could be a source of problems.

Next, you may be queried as to which storage devices are installed. This occurs only when there are no configuration switches available, such as with a TM990/102 or SBC95/1 A single 'Y' character selects the device. system. Anything else ignores the device.

Finally, the PDOS boot menu is displayed. You may now select from various functions including:

- System boot from disk numbers 0 through 1. 99. Boot sector constants within the EPROMs select the correct sector of the boot. Auto-boot selects the lowest numbered storage device.

- 2. System memory test. A pass is made through memory writing random data and then a second pass verifies memory content.

- з. Memory inspect and change. System memory is examined, altered, or copied. Both a hex and an ASCII dump is provided.

- 4. BOOT and MAKE BOOT routines. A system boot from any logical sector is done by the boot routine. The MAKE BOOT routine writes memory from >0000 to >6000 to any disk # and logical sector.

9902 initialized for 11 bits: 1 start bit 7 bit character 1 even parity 2 stop bits

(LOAD vector) (carriage return) SELECT TM990/303? Y {Optional} SELECT ER3314? {Optional} \*PDOS BOOT R2.4 0-99=800T 100=MEMORY TEST 101=IAC 102=B00T 103=MAKE BOOT 104=AUX ?

System boot

Memory test

Memory inspect and change

Boot and make boot

PAGE 2-11

(2.2.2 BOOT EPROMS continued)

AUX programs. Other routines are 5. placed in the lower EPROMs (>FOOO through >F7FF) and called via an entry at >FOOD with the AUX selection.

Auxiliary programs

#### BOOT MEMORY TEST

Option 100 of the boot EPROMs selects a memory test routine. An optional second decimal parameter is used to select a memory test range other than from >0000 to >7000. The routine first passes through memory, writing random data. A second pass is then made to verify the data. For each successful memory pass, a period is output to the console. If an error occurs, the address is printed along with the exclusive OR of the data read and the correct data.

| ?100,57312 | Tests >0000->E000 |

|------------|-------------------|

| ?100,53216 | Tests >0000->0000 |

| ?100,49120 | Tests >0000->C000 |

| ?100,45024 | Tests >0000->8000 |

| ?100,40928 | Tests >0000->A000 |

| ?100,36832 | Tests >0000->9000 |

| ?100,32736 | Tests >0000->8000 |

.

#### AUTO-BOOT

The PDOS boot EPROMs have the facility to automatically boot PDOS into RAM and set the auto-start flag at memory address >0070. On a TM990/101MA system, this option is selected by switch #1 on the CPU card. Other systems require external switches or hard coded auto-boot.

#### AUTO-START

If the auto-start flag (byte >0070) is nonzero, then PDOS automatically executes the file named 'SY\$STRT' on the system disk. Care must be taken that a baud port command of some type is executed under control of the 'SY\$STRT' file, since the system console port is not auto-bauded.

The file type of 'SY\$STRT' indicates how the file is to be executed. Normally, it would be a procedure file with the first command being a BAUD PORT (BP) for the console port. Other commands could include configuring other user tasks and the starting of a turn-key application program. The auto-start file name is changed by the BFIX utility.

Switch 1 ON = Auto boot

.SA SY\$STRT,AC .SF SY\$STRT BP 1,19200 BP 2,9600 SY 1 LV 10 MENU RC •\_\_

32222222222222222222222

PDOS 2.4 DOCUMENTATION

CHAPTER 2 INSTALLATION

PAGE 2-12

(2.2.2 BOOT EPROMS continued)

### SYSTEM DISK

>0070 = Auto-run flag >0071 = Initial default disk #

Location >0071 is loaded with the boot disk number after the system is booted and just before a 'BLWP a>0000' is executed. PDOS loads the default system disk number from this location. Thus, the system comes up using the same disk from which it was booted.

#### 2.3 PDOS SUPPORTED HARDWARE

2.3.1 CPU

#### CHAPTER 2 INSTALLATION

#### 2.3.1.1 SBC 95/1 CPU

The SBC 95/1 is a single-board computer which offers 16-bit minicomputer performance at a very low cost, in a format suitable for most industrial control applications. STD Bus compatibility assures that a wide variety of support products are immediately available.

Some of the outstanding features of the SBC 95/1 include:

- STD Bus compatible.

- Standalone capability.

- Uses 12 MHz TMS9995 third-generation microprocessor.

- On-board 8K-16K byte EPROM.

- On-board 4K byte RAM.

- 2 software selectable memory maps

- 2 Async serial ports.

- Single +5 volt operation (except RS232).

- 8-bit TTL input port, 5-bit TTL output port.

The SBC 95/1 PDOS is shipped with a TMS2532 EPROM containing the read/write sector routines and boot utilities. A 74S472 PROM is also included which contains the PDOS memory map. Since the RESTART vector (>FFFC) is in CPU RAM, the boot EPROM must be initially in low memory and contain the RESTART vector (>0000). Once initialization has occurred, the EPROM is mapped high to address >F000 through >FFFF for PDOS operation.

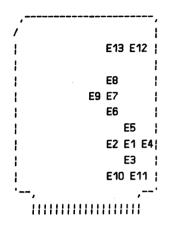

The boot EPROM is installed in the 28-pin socket U9 on the CPU card. The 74S472 PROM is installed in the 20-pin socket U8. The 'auto first wait state' jumper N (E35-E36) should be removed.

It is necessary to have one momentary closed switch to ground connected to PBRESET- (pin 48) on the STD bus. This is used to reset the 9995 and initiate the boot ROM program. An optional momentary closed switch to ground is connected to NMIRQ- (pin 46). This switch restarts PDOS without having to reboot the system. The boot ROM places the vector  $\partial > 0000$  in the NMI location >FFFC.

The correct jumper settings for PDOS to operate with the SBC 95/1 CPU are:

| E1-E2, E4-E5             | U9 = 2532 EPROM      |

|--------------------------|----------------------|

| E8-E9, E10-E11, E13-E14  | U10 = 4015 RAM       |

| E17-E18,E19-E20, E22-E23 | U11 = 4016 RAM       |

| E26-E27                  | PORT A RS232         |

| E29-E30                  | PORT B RS232         |

| E31-E32                  | Port B -cts to gnd   |

| E33-E34                  | PORT B -DTR FROM P20 |

TMS9995 STD BUS CPU

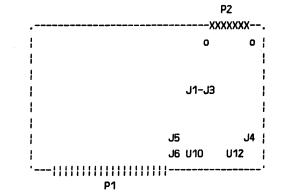

| P2             | JUMPERS: |            |  |  |

|----------------|----------|------------|--|--|

| ,11111111      | ,,       |            |  |  |

| / 0            | I        | B=4,5,6    |  |  |

| † E            | J        | C=7,8,9    |  |  |

| I GH           | 1        | D=10,11,12 |  |  |

| ; F            | L¦       | E=13,14,15 |  |  |

| I              | K ¦      | F=16,17,18 |  |  |

| ; CD           | ł        | G=19,20,21 |  |  |

| ¦ B            | 1        | H=22,23,24 |  |  |

| U8 A U9 U10 U1 | 11       | I=25,26,27 |  |  |

| N              | M I      | J=28,29,30 |  |  |

| 1              | 1        | K=31,32    |  |  |

| ',             | ,'       | L=33,34    |  |  |

|                | M=35,36  |            |  |  |

|                |          | N=37,38,39 |  |  |

1-TMS2532 EPROM 1-745472 PROM

RESET switch RESTART switch

PAGE 2-14

## 2.3.1.2 TM990/101MA CPU MODULE

The Texas Instruments TM990/101MA is a self-contained microcomputer on a single printed-circuit board. Its features include a central processing unit (CPU) with hardware multiply and divide, programmable serial and parallel I/O lines, external interrupts, three programmable interval timers, and onboard RAM and EPROM.

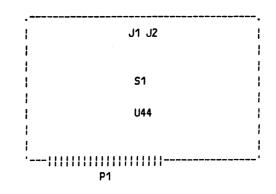

The TM990/101MA PDOS is shipped with 2 2708 EPROMs containing the read/write sector routines and boot utilities. PDOS requires the TM990/101MA onboard EPROM to be addressed high and the onboard RAM to be addressed low. The two 2708 boot EPROMs are inserted into sockets U43 and U45 as indicated on the EPROMs. The following jumpers must be in place on the CPU card for a RAM system:

| Function           | Stake Pins Used |

|--------------------|-----------------|

| HI/LO memory map   | E15-E16         |

| Interrupt 4 source | E2-E3           |

| Interrupt 5 source | E5-E6           |

| EPROM enable       | E13-E14         |

| SION EPROM         | E8-E53          |

| 2708/2716 map      | E10-E11         |

|                    | E27-E28,E29-E30 |

-E6 3-E14 -E53 0-E11

E32-E33,E34-E35

The Data Terminal Ready (DTR) signal must be present on all console ports. This is hardwired by presenting pin 5 to pin 20 on the port connector.

The CPU RESTART.B capacitor should be installed on the CPU card to filter (effectively debounce) the -RESTART.B signal. A 39 microfarad capacitor at C23 is the suggested value for manual actuation by a SPST pushbutton to ground. (See Section 6.7.3 of TM990/101MA manual.)

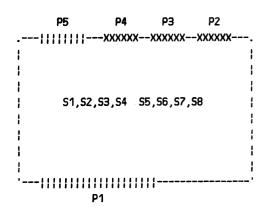

The TM990/101MA CPU ID DIP-switch is used by the READ/WRITE SECTOR EPROMS to configure the system according to the hardware storage devices 'attached. These are presently defined as follows:

| S1 = ON | AUTO BOOT and AUTO EXECUTE OF 'SY\$STRT' |

|---------|------------------------------------------|

| S2 = ON | TM990/303A Controller (Disks 0-3)        |

| 53 = ON | ER3314 Winchester Controller (Disks 4-7) |

| S4 = ON | TM990/210 6 Bubble (Disks 8-11)          |

| S5 = ON | ER3300 Floppy Controller (Disks 12-127)  |

TM990/100MA CPU module

PDOS system

RAM 10H INT4 on INTE on EPROM enabled Fast EPROM 2708

DTR high

Power on RESTART.B capacitor

|                                      | Auto E | Boot  |     |       |            |

|--------------------------------------|--------|-------|-----|-------|------------|

| /                                    | Units  | 0-3   | =   | 303A  | Floppy     |

| · · · //                             | Units  | 4-7   | I   | 3314  | Winchester |

| ///                                  | Units  | 8-11  | =   | 210 E | Bubble     |

| ////                                 | Units  | 12-99 | =   | 3300  | Floppy     |

| /////                                |        |       |     |       |            |

| P4 ////                              | F      | Э     |     | P2    |            |

| ////                                 | XX)    | XXXX  | -XX | XXXX  | (          |

| ////                                 |        |       |     |       | 0          |

| 1////                                |        |       |     |       | 1          |

| S12345                               |        |       |     |       | 1          |

| 1                                    |        |       | U   | 45    | 1          |

| 1                                    |        |       | U   | 44    | 1          |

|                                      |        |       | U   | 43    | 1          |

| 8                                    |        |       | U   | 42    | -          |

| ''!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |        |       |     |       |            |

| P1                                   |        |       |     |       |            |

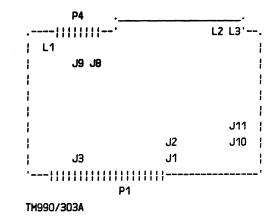

#### 2.3.1.3 TM990/102 CPU MODULE

The TM990/102 CPU module is a single board computer which features the TMS9900 CPU, 128K bytes of dynamic RAM, a programmable serial port, two programmable interval timers, and up to 16k bytes of EPROM. The extended address lines XAO through XA3 are also supported such that up to a megabyte of memory can be added to the system. PDOS supports up to 512K bytes.

The TM990/102 PDOS is shipped with two 2516 EPROMs containing the read/write sector routines and boot utilities. The two EPROMs are installed in sockets U10 and U12. The 102 jumpers are configured as follows for the 2516's:

| J1 | OUT = EPROM ON |

|----|----------------|

| J3 | IN = 2516      |

| J4 | 1-2 = 2516     |

| J5 | 2-3 = 2516     |

| J6 | 2-3 = 2516     |

Since the TM990/102 CPU card does not have any DIP switches, the PDOS boot EPROMs prompt for each mass storage device after auto-bauding but before the boot menu. A single 'Y' character selects the device for use by PDOS. Selected devices are stored at memory location >2FFE and tested before each sector access. An error 100 results from access to a non-selected device.

Auto-boot is available only by programming new EPROMs. Тно methods of auto-boot are available for the 102. First, if the ABFLG of the boot EPROMs is set, then the system always auto-boots. Second, if the SWFLG is set, then the DIP switches on a TM990/307 card are sampled for both auto-boot and device selection.

PDOS 102 defines eight 9902 console ports. Port #1 is the system console port and is on the TM990/102 CPU card. The other 9902 ports are dependent upon additional hardware. A TM990/303B has an RS232 port which is addressed at location >0180 and used for port #2, and other ports obtained from TM990/307 I/O extender cards.

TM990/102 CPU module:

SELECT TM990/303? Y SELECT ER3314? \*PDOS BOOT R2.4 0-99=B00T 100=MEMORY TEST 101=IAC 102=B00T 103=MAKE BOOT 104=AUX ?\_

PORT #1 >0080 P2 TM990/102 PORT #2 >0180 PORT D TM990/307 PORT A TM990/307 PORT #3 >0500 PORT #4 >0580 PORT B TM990/307 PORT #5 >0600 PORT C TM990/307 PORT A TM990/307 PORT #6 >0680 PORT #7 >0700 PORT B TM990/307 PORT #8 >0780 PORT C TM990/307 DRIVER >0800 PORT D TM990/307

PDOS 2.4 DOCUMENTATION

(2.3.1.3 TM990/102 CPU continued)

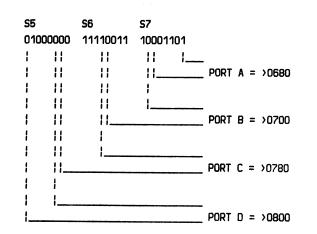

One or two TM990/307 cards may be used in conjunction with the TM990/102 CPU. Ports #2, #3, #4, and #5 would be on the first TM990/307 board and ports #6, #7, and #8 on the optional second 307 board. The remaining port of the second TM990/307 card would be used for drivers, such as a modified \$TTA.

If a TM990/303B supplies an RS232 port at base >0180, then port D of the first TM990/307 board should be changed to >0680. An optional second TM990/307 would then have port A changed to >0880 and used for a driver.

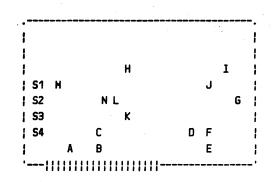

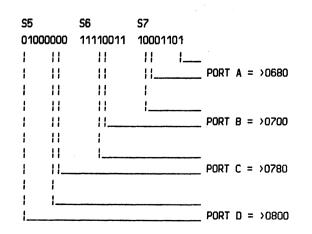

If TM990/307 cards are used in conjunction with the TM990/102 card, then the 307 switches should be set as follows:

- 1) Both TM990/307 cards are for set interrupt level 8. For the 1st TM990/307, switch packs S1 through S4 are set with switch 1 ON and switches 2-8 OFF. (See figure 2-2 of 307 manual.) For the 2nd TM990/307, switch packs S1, S2, and S3 have switch 1 ON and 2-8 OFF. Switch pack S4 has switches 1-8 OFF.

- 2) The first TM990/307 board is set with CRU base addresses >0500, >0580, >0600, and >0180.

- 3) The second TM990/307 board, if used, is set with CRU base addresses of >0680. >0700, >0780, and >0800 (not used).

Optional PDOS 102 boot EPROMs which use DIP switches for auto-boot and device selection (SWFLG EQU 1) look to the first TM990/307 switch pack S8. These switches are defined as follows:

> SW8 OFF = AUTO BOOT SW7 OFF = TM990/303A (disks 0-3) SW6 OFF = ER3314 INSTALLED (disks 4-7) SW5 OFF = TM990/210 BUBBLE (disks 8-11)

Note #1: The 'sense' of these switches is opposite that found on the TM990/101M card. An 'OFF' (OPEN) indicates the feature is selected.

Note #2: In order for the TM990/102 to use the configuration switches on the first TM990/307 card, the CRU base addresses for ports A and B MUST be at >0500 and >0580 respectively. The system will not work if this is not correct.

TM990/307 RS232 EXPANSION CARD:

TM990/307 card #1 switch packs:

TM990/307 card #2 switch packs:

2.3.2 MEMORY

#### 2.3.2.1 ER3232 32K STATIC RAM

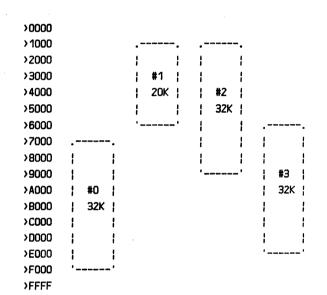

The ER3232 is a 32K byte static RAM module. Each module is CRU page selectable and has an optional RS232C I/O port. Only one CRU instruction is required to switch from one memory plane to another. Memory mappings provide for single and multiple board PDOS memory configurations.

Switches S3 and S4 select four different memory maps. One is for a 20K byte system page and the other three are for full 32K byte RAM systems. These switches also select the CRU bases for the paging latch and the RS232C port. The following are the map switch definitions:

| SELECT | S3, S4  | MEMORY ADDR | PAGE CRU | RS232 CRU |

|--------|---------|-------------|----------|-----------|

|        |         |             |          |           |

| #0     | ON, ON  | >7000->EFFF | >980     | >A00->BC0 |

| #1     | ON,OFF  | >1000->5FFF | >D80     | >E00->FC0 |

| #2     | OFF,ON  | >1000->8FFF | >D80     | >E00->FC0 |

| #3     | OFF,OFF | >6000->DFFF | >980     | >AOO->BCO |

Switches S5, S6, and S7 specify the page number. Up to eight memory pages may reside at the same memory address. The page CRU base is used to select one memory plane while deselecting all others. This greatly facilitates memory swapping for multiple users. These switches also determine the CRU base for the optional RS232C port thus allowing new users to be added to a PDOS system with their own console terminal. The following are the page switch definitions:

|            |              | RS232C         | CRU BASE |

|------------|--------------|----------------|----------|

| PAGE       | S5,S6,S7     | S3=S4          | S3<>S4   |

|            |              |                |          |

| <b>#</b> 0 | ON, ON, ON   | >A00           | >E00     |

| #1         | ON, ON, OFF  | >A40           | >E40     |

| #2         | ON,OFF,ON    | >A80           | >E80     |

| #3         | ON, OFF, OFF | >ACO           | >ECO     |

| #4         | OFF,ON,ON    | >800           | >F00     |

| <b>#5</b>  | OFF,ON,OFF   | <b>&gt;B40</b> | >F40     |

| #6         | OFF,OFF,ON   | >880           | >F80     |

| #7         | OFF,OFF,OFF  | >BCO           | >FCO     |

|            |              |                |          |

Finally, switch S8 selects one memory wait state if slow static RAM is used. Normally, RAMs with access times of 450 nanoseconds or less do not require a memory wait state. One memory wait state is selected by setting S8 OFF (open). S8 ON (closed) disables any wait states.

| LI R12,>980 | ;POINT TO PAGE SELECT |

|-------------|-----------------------|

| LI RO,>0300 | ;GET PAGE 3 SELECT    |

| LDCR R0,3   | ;SELECT PAGE 3        |

| XXXXXXX                              |    |   |

|--------------------------------------|----|---|

| 1                                    |    | 1 |

| 1                                    |    | 1 |

| 1                                    |    | 1 |

| 1                                    |    | ł |

| 54                                   | 58 | 1 |

| <b>;</b> S3                          | S7 | 1 |

| ; S2                                 | S6 | 1 |

| 51                                   | S5 | 1 |

| '!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |    | ' |

| P1                                   |    |   |

S8 OFF = one memory wait state

### CHAPTER 2 INSTALLATION

PAGE 2-18

####

#### 2.3.2.2 MATRIX 7911/RPC 32K STATIC RAM

The MATRIX 7911/RPC is a 32K byte static RAM card that conforms to all STD BUS standards and is used in conjunction with the SBC 95/1 CPU card.

The address lines are decoded into 16 4K byte blocks. Each 4K byte block of memory may be addressed at any 4K byte boundary by means of wire wrap jumpers between J2 and J4, and J3 and J5. Each connection on J4 and J5 corresponds to its numbered block of memory, and each connection on J2 and J3 corresponds to a decoded 4K byte address space. J2 decodes 8 4K blocks of address space for >0000 to >7FFF and J3 decodes 8 4K blocks of address space for >8000 to >FFFF.

A SBC 95/1 - PDDS environment handles one or two 7911/RPC cards. The first card is addressed from >0000 to >7FFF and the second from >8000 to >DFFF. This is done as follows:

| 1st card: | J2/0 - J4/1         | >0000->0FFF |

|-----------|---------------------|-------------|

|           | J2/1 - J4/2         | >1000->1FFF |

|           | J2/2 - J4/3         | >2000->2FFF |

|           | J2/3 - J4/4         | >3000->3FFF |

|           | J2/4 - J4/5         | >4000->4FFF |

|           | J2/5 - J4/6         | >5000->5FFF |

|           | J2/6 - J4/7         | >6000->6FFF |

|           | J2/7 - J4/8         | >7000->7FFF |

| 2nd card: | J3/8 - J5/1         | >8000->8FFF |

|           | <b>J3/9 - J</b> 5/2 | >9000->9FFF |

|           | J3/10 - J5/3        | >AOOO->AFFF |

|           | J3/11 - J5/4        | >B000->BFFF |

|           | J3/12 - J5/5        | >COOO->CFFF |

|           | J3/13 - J5/6        | >D000->DFFF |

The 7911/RPC memory card is used in "primary" map mode. This is enabled by installing a jumper between pins 1 and 2 of J1. MATRIX 32K STATIC RAM

| ,  |      |    |    | ,    |

|----|------|----|----|------|

| 1  |      |    | J5 | J4   |

| 1  |      |    | JЗ | J2 ¦ |

| 1  | 1B   |    |    | 1    |

| 1  | 1A   | 4A |    | 4B   |

| ł  | 2B   | 5A |    | 58   |

| ł  | ZA   | 6A |    | 6B   |

| ł  | 3B   | 7A |    | 7B ¦ |

| 1  | ЗА   | 8A |    | 8B   |

| ł  |      |    |    | 1    |

| ł  |      |    |    | J1   |

| '- | -,   |    |    | ,'   |

|    | 1111 |    |    |      |

### 2.3.2.3 TM990/201 STATIC RAM

TM990/201 and TM990/206 RAM cards can be used to provide contiguous RAM memory for a PDOS system. However, they do require a modified decode PROM in socket U44 such that contiguous memory exists from >0000 to at least >8000.

#### TM990/201 EPROM/RAM CARD

|                                                    |                                                                       | بدور جور جور جور جور میں میں جارے ہیں جوار براز زیار جوں جور جور جور                |                                                                                            |                                                                                                   |

|----------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| <br>ه هه چه ها | ، حتين حتين حتين حتين جمل خلك خلك حتك حتك حتين جين وان كتيد حان حدد د | ده ميد خله عنه دين هي خين خين خين تين <del>عن خين خين تين خين خين تين خين خين</del> | خیل جلی حق طل کار برید برند جبه بعد جنه جنه جنه جنه جنه حبه جنه طل خل خل خل خل خل خل خل خل | بد: هذه هاه ها هية دينا ها: ها ها عليه بلين عليه في في عنه عنه عن خو غل عليه عن ها عليه عنه ها: « |

|                                                    |                                                                       |                                                                                     |                                                                                            |                                                                                                   |

|                                                    |                                                                       |                                                                                     |                                                                                            |                                                                                                   |

PAGE 2-20

PDOS 2.4 DOCUMENTATION

### 2.3.2.4 TM990/203A DYNAMIC RAM

The TM990/203 line of memory expansion boards are designed to expand system memory from 64K to 256K bytes. The TM990/203 module works only with the TM990/101MA series while the TM990/203A provides expanded memory for the TM990/102 and TM990/103 CPU modules.

|    |     | _   |          |    | _     |      |         |         |      |        |           |     |      |

|----|-----|-----|----------|----|-------|------|---------|---------|------|--------|-----------|-----|------|

|    |     | A = | E4-E5    |    | Rese  | t pa | arity   | interru | upt  |        |           |     |      |

|    |     |     | E8-E9 OL | IT | Disal | ble  | parit   | y inter | rrup | t      |           |     |      |

|    |     | B = | E13-E14  |    | Sele  | ct I | RAM si  | ze (-2) | )    |        |           |     |      |

|    |     | C = | E16-E18  |    | Sele  | ct I | RAM si: | ze      |      |        |           |     |      |

|    |     |     | E20-E22  |    | Sele  | ct I | RAM si  | ze      |      |        |           |     |      |

|    |     | D = | E23-E24  |    | Memor | ry i | wait s  | tate    |      |        |           |     |      |

|    |     | E = | E27-E28  |    | Memor | ry i | wait s  | tate    |      |        |           |     |      |

|    |     | F = | E31-E34  |    | Numb  | er ( | of ref  | resh cy | ycle | S      |           |     |      |

|    |     | G = | E45-E65  |    | Cycle | e-s  | teal r  | efresh  |      |        |           |     |      |

|    |     | н = | E47-E48  |    | Size  | of   | memor   | y devi  | ce   |        |           |     |      |

|    |     | I = | E73-E74  |    | Early | y/1a | ate ME  | MCYC-   |      |        |           |     |      |

|    |     | J = | N/I      |    | Sele  | ct a | applic  | ation   |      |        |           |     |      |

|    |     | к = | E82-E83  |    | THS4  | 116  | devic   | e used  |      |        |           |     |      |

|    |     | L = | E84-E85  |    | Sele  | ct i | nemory  | speed   |      |        |           |     |      |

|    |     | M = | E90-E91  |    | Sele  | ct ' | 15-bit  | addres  | 5S   | (E89-E | <b>90</b> | for | 102) |

|    |     |     | E93-E94  |    | Sele  | ct · | 15-bit  | addres  | 55   | (E92-E | 93        | for | 102) |

|    |     | N = | E36-E39  |    | Sele  | ct · | 15-bit  | addre   | 55   | (E36-E | 37        | for | 102) |

|    |     |     |          |    |       |      |         |         |      |        |           |     |      |

|    |     | ·   | •        | •  |       |      | •       |         |      |        |           |     |      |

| ON | (0) | 1   | 1        | X  | хх    | 1    | 1       |         |      | >      | (         | 1   |      |

|    |     |     |          | 1  |       |      |         |         | •    |        |           |     |      |

### OFF (1) | X X X X | X | X X X X | X X X | X X X | **S1**

S2

**S4**

S3

TM990/203A DYNAMIC RAM

**~~~~~**

### 2.3.3 SECONDARY STORAGE

### 2.3.3.1 ER3300 FLOPPY CONTROLLER

The ER3300 floppy controller module supports large and small floppy disk drives. The board also includes three RS232C I/O ports with full modem capability. The board is referenced by PDOS as disk devices 12 through 15.

The floppy edge connector pins are defined as follows:

P5-2 -MOTOR ON #1 -MOTOR ON #2 P5-4 P5-6 -HEAD SEL P5-8 -IP P5-10 -SELECT #0 P5-12 -SELECT #1 P5-14 -SELECT #2 P5-16 -MOTOR ON #0 P5-18 -DIRECTION P5-20 -STEP P5-22 -WRITE DATA P5-24 -WRITE CLOCK P5-26 -TRACK 00 P5-28 -WRITE PROTECT P5-30 RAW DATA P5-32 -MOTOR ON #3 P5-34 -SELECT #3 P5-36 -HEAD LOAD P5-38 READY P5-40 -WRITE FAULT P5-1 thru 39 GND

ER3300:

PAGE 2-21

ER3300A:

TMS9901 CRU addresses are as follows:

>0400->043F >0440->047F

1793 floppy controller register memory map addresses are as follows:

- >E001 = Status Register

- >E003 = Read Track

- >E005 = Read Sector

- >EOO7 = Read Data

- >E009 = Command Register

- >EOOB = Write Track

- >EOOD = Write Sector

- >EOOF = Write Data

PDOS 2.4 DOCUMENTATION

#### 2.3.3.2 ER3314 WINCHESTER INTERFACE

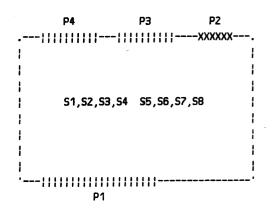

The ER3314 interface is a multipurpose hardware interface board for integration of a Winchester hard disk into the PDOS system. The I/O port provides an interface to Shugart Associates System Interface (SASI) SA1400 series intelligent disk controllers. Also available on the board are two fully functional IEEE 488-1978 controller / talker / listener ports. The main bus connector of the board is compatible with the TM990 bus specification in all respects.

The SASI interface may be operated in either the programmed I/O mode or in the direct memory access (DMA) mode. The IEEE 488-1978 ports (also referred to as GPIB ports) may operate as either polled or interrupt driven devices. The GPIB ports have no DMA capability.

The interface card occupies one slot of the processor chassis. Connection to the CPU is via the TM990 standard bus. The GPIB ports are terminated in standard GPIB connectors. The SA1400 cable should be terminated in a 50-pin SCOTCHFLEX 3425-5000 or equivalent connector to mate with the interface card connector (SCOTCHFLEX 3433-1002).

Data transfers to and from the GPIB ports are byte oriented. The SASI interface is also byte oriented when transfers are done under program control. Data transfers are word oriented when the SASI interface is operating in DMA mode. Byte oriented transfers to any of the three ports are done through the most significant byte (DO-D7) of the TM990 bus.

Switch packs SW1 and SW2 control address and operation of GBIP ports P4 and P3 respectively. Switch positions are defined as follows:

> 1-5 = Port address (0-31) (ON=0, OFF=1) 6 ON = Tristate outputs 6 OFF = Open collector outputs

The extended address drive capability is enabled with a jumper from XA to EN and disabled with a jumper from XA to OF. XAO through XA3 determine the extended address states.

Winchester hard disk

2 IEEE 488-1978 interfaces

Programmed I/O or DMA

Standard GPIB connectors

Byte oriented transfers

ER3314:

| P4      | P3    |     | P2    |     |

|---------|-------|-----|-------|-----|

| XXX     | xxxxx |     | -     |     |

| 1       |       |     |       | 1   |

| 1       |       |     |       | 1   |

| l S     | W1    |     |       | 1   |

| l S     | W2    |     |       | 1   |

| 1       |       | XAO |       | - 1 |

| 1       |       | XA1 | XA-OF | 1   |

| 1       |       | XA2 | 1     | 1   |

| 1       |       | ХАЗ | EN    | 1   |

| '!!!!!! |       | 111 |       | '   |

|         | P1    |     |       |     |

PAGE 2-23

#### (2.3.3.2 ER3314 WINCHESTER INTERFACE continued)

The Winchester device service routine (BT3314:SR) is shipped with logical device numbers 0 and 1 accessing the Winchester, and device numbers 2 and 3 accessing floppies. The boot EPROMs translate these to disk numbers 4 through 7 respectively. The ER3314 interface is selected by switch #3 of the CPU card.

Disk #4 selects the first half of a SA1004 10 megabyte Winchester and disk #5 the second half. Disk #6 is initialized for a SA800 single sided floppy drive or equivalent. Disk #7 is initialized for a SA850 double sided floppy drive.

If you have a SA1002 instead of a SA1004, then disk #4 accesses the complete disk. Depending on the floppy type (single or double sided), the floppy drive should be connected as logical unit 2 or 3. After the PDOS disks have been transferred to the Winchester, the drives are configured as desired.

The error numbers returned from the ER3314 device service routine (BT3314:SR) range from 200 to 299. They are defined as follows:

> 201 = No Index Signal Detected 202 = No Seek Complete Detected 203 = Write Fault 204 = Drive Not Ready 205 = Drive Not Selected 206 = No Track 000 Detected

216 = ID Field ECC or CRC error 217 = Data Field ECC or CRC error 218 = ID Address Mark Not Found 219 = Data Address Mark Not Found 220 = Record Not Found 221 = Seek Error 222 = DMA Timeout Error 223 = Write Protected 224 = Correctable Data Field ECC error 225 = Bad Sector Found 226 = Format Error

232 = Invalid Command received from Host 233 = Illegal Logical Sector Address

Disk #4 and #5 = SA1004 Winchester

Disk #6 = SA800 single sided floppy

Disk #7 = SA850 double sided floppy

S3 on = ER3314 Winchester system

ER3314 error numbers

### (2.3.2.2 ER3314 MINCHESTER INTERFACE continued)

### ER3314 memory mapped addresses are defined as follows:

#### Memory mapped addresses

| ADDRESS                          | READ                                                                         | MRITE STATE            |

|----------------------------------|------------------------------------------------------------------------------|------------------------|

|                                  | DATA FROM SA1400<br>STATUS FROM SA1400                                       | <br>DATA TO SA1400<br> |

| >E040<br>>E042<br>>E044          | PORT 1 INTRPT STATUS 0<br>PORT 1 INTRPT STATUS 1<br>PORT 1 ADDRESS STATUS    |                        |

| >E046<br>>E048<br>>E04A<br>>E04C | PORT 1 BUS STATUS<br>PORT 1 ADDRESS SHITCH 1<br><br>PORT 1 CHND PASS THROUGH | PORT 1 SERIAL POLL     |

| >E04E<br>>E050                   | PORT 1 DATA IN<br>PORT 1 ADDRESS SWITCH REG                                  | PORT 1 DATA OUT        |

| >E062<br>>E064                   | PORT 2 INTRPT STATUS 0<br>PORT 2 INTRPT STATUS 1<br>PORT 2 ADDRESS STATUS    | PORT 2 INTRPT MASK 1   |

| >E066<br>>E068<br>>E06A<br>>E06C | PORT 2 BUS STATUS<br>PORT 2 ADDRESS SHITCH 1<br><br>PORT 2 CMND PASS THROUGH | PORT 2 SERIAL POLL     |

| >E06C<br>>E06E<br>>E070          | PORT 2 DATA IN<br>PORT 2 ADDRESS SWITCH REG                                  | PORT 2 DATA OUT        |

#### ER3314 CRU addresses are defined as follows:

CRU addresses

| ADDRESS     | CRUIN               | CRUOUT        |

|-------------|---------------------|---------------|

|             |                     |               |

| >0480       | SA1400 BUSY         | SA1400 RESET  |

| >0482       | SA1400 MESSAGE      | SA1400 SELECT |

| >0484       | SA1400 COMMAND/DATA | DMA MODE      |

| >0486       | SA1400 REQUEST      |               |

| >0488       | SA1400 INPUT/OUTPUT | XA3           |

| >048A       | SA1400 STATUS VALID | XA2           |

| >048C       | SA1400 MSG COMPLETE | XA1           |

| >048E       |                     | XAO           |

| >04C0->04FF | TMS 9911            | TMS 9911      |

|             |                     |               |

### CHAPTER 2 INSTALLATION

PDOS 2.4 DOCUMENTATION

### 2.3.3.3 GW3 FDC/1 FLOPPY CONTROLLER

The FDC/1 floppy disk controller board is an advanced mass storage controller for STD Bus computer systems. The FDC/1 is tailored for operation with GW3's SBC 95/1 processor board using the high performance TMS 9995. Important freatures include:

- 8" or 5" drive support, software selectable

- Single or double sided, single or double density

- Phase-lock-loop data separator

- High speed DMA data transfers

Either an 8" or 5" floppy drive is directly connected to the P2 connector of the FDC/1 without need for pinout adaptors or jumper changes on the board. Four 8" or three 5" drives may be daisy-chained from a single controller board. (8" and 5" drives may be intermixed on the same cable!) All controler commands and status are I/O mapped into an 8 byte block.

Although the drive size, side, and density are software selectable, a single jumper allows the drive size to be forced to 8" or 5" or software select. The position of the jumper can be read by software allowing OEM applications to automatically adapt to the final configuration.

Only two jumpers are required for operation of the FDC/1 board with the PDOS BTFDC1:SR DSR, namely:

> Select >EFC0 base address E1-E2 E6-E8 Select 8" drive

#### GW3 FDC/1 FLOPPY CONTROLLER

PDOS 2.4 DOCUMENTATION

#### 2.3.3.4 TM990/210 BUBBLE MEMORY

The TM990/210 Bubble Memory Module provides non-volatile bubble memory storage for the PDOS system. Access time is from 860 microseconds minimum to 7.3 milliseconds maximum per sector. PDOS configures a 6 bubble module as a single disk, complete with directory and file storage.

Switch 4 on the CPU card is used to indicate that TM990/210 card(s) are in the system beginning at memory address >E100. Up to 4 boards are supported (disk numbers 8 through 11) and are addressed in 32 byte increments. A TM990/210-3 has 6 MMU's (Memory Module Unit) with 69k bytes of storage.

The bubble is accessed in single page mode. This allows interrupts and other system functions to proceed while the bubble is being accessed. One PDOS sector (256 bytes) consists of 15 pages. Each bubble contains 42 sectors for a total of 42 x 6 = 252 sectors. The bubble can be configured for a boot module, leaving 156 sectors for program storage.

Note: Use jumper P3A to P3B to avoid bubble reference problems cause by IORST.

Units 8 thru 11 = Bubble

S4 ON = TM990/210-3 bubble modules

Unit 8 = 2>E100 Unit 9 = @>E120 Unit 10 = a > E140Unit 11 = 2>E160

Single page mode

15 pages/sector 42 sectors/bubble 6 bubbles/card = 252 sectors

Boot = 0-155 File storage 156-251 Boot

Address >E100 => XADDR SO = ON S1 = ONS2 = ONS3 = ONXAEN = OFFADDR SEL SO = OFFS1 = OFFS2 = OFFS3 = ONS4 = ONS5 = ONS6 = ONS7 = OFFS8 = ONS9 = ON

S10 = 0N

| <b>\$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ </b> |                        | . 해 해 해 해 해 해 해 해 해 해 해 해 해 해 해 해 해 해 해 |

|------------------------------------------------------------------|------------------------|-----------------------------------------|

| PDOS 2.4 DOCUMENTATION                                           | CHAPTER 2 INSTALLATION | PAGE 2-27                               |

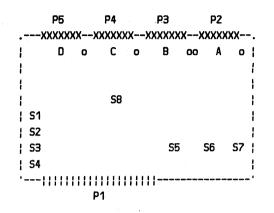

### 2.3.3.5 TM990/303A FLOPPY CONTROLLER

The TM990/303A is a Texas Instruments Inc. floppy disk controller module. This board provides a controlling interface between the microcomputer and an 8 inch floppy disk drive. The POOS device service routine (BT303:SR) initializes the TM990/303A for 8 inch, IBM, single or double sided, double density format. The TM990/303A board is selected by switch #2 on the TM990/101MA CPU card and is addressed by PDOS as disk numbers 0 through 3. The TM990/102 CPU selects the TM990/303A by answering the device prompt with a 'Y'.

STEP 1 - JUMPER SETTINGS

The TM990/303A should be jumpered as follows for a standard drive system:

| J1 = E1-E3    | No boot load      |

|---------------|-------------------|

| J2 = E5-E6    | 44 44 14          |

| J3 = INT2     | Interrupt level 2 |

| J8 = IN       | Disk format       |

| J9 = IN       | Disk size         |

| J10 = STD     | Standard 8" disk  |

| J11 = E16-E17 | N N N             |

Suggested Shugart SA800 disk drive jumper settings are listed in TABLE 2-2 of the TM990/303A manual. These must be set correctly for proper system initialization.

STEP 2 - CARD CAGE

When using a TM990/510 or equivalent, the etch on the backplane between lines 95 and 96 must be open (cut) where the TM990/303A board is installed. Generally, this slot is the closest to the bus termination.

#### STEP 3 - ATTACH DRIVE and TEST

When system installation has been checked and verified, power can be applied. With power applied, the controller executes a self-test. LEDs L2 and L3 go on. When the test is complete, these go off and L1 remains on, indicating no error.

SHUGART SA800 jumper settings

| Jumper  | Intermediate   | Terminated |  |  |

|---------|----------------|------------|--|--|

| Name    | Board          | Board      |  |  |

|         |                |            |  |  |

| Α       | IN             | IN         |  |  |

| В       | IN             | IN         |  |  |

| C (P18) | IN             | IN         |  |  |

| D       | OUT            | OUT        |  |  |

| DC      | IN             | IN         |  |  |

| DDS     | OUT            | OUT        |  |  |

| DS      | IN             | IN         |  |  |

| DS1     | Drive O select |            |  |  |

| DS2     | Drive 1 select |            |  |  |

| DS3     | Drive 2 select |            |  |  |

| DS4     | Drive 3 select |            |  |  |

| HL      | OUT            | OUT        |  |  |

| т1      | OUT            | IN         |  |  |

| T2      | IN             | IN         |  |  |

| T3      | OUT            | IN         |  |  |

| T4      | OUT            | IN         |  |  |

| T5      | OUT            | IN         |  |  |

| T6      | OUT            | IN         |  |  |

| х       | OUT            | OUT        |  |  |

| Y       | OUT            | OUT        |  |  |

| Z       | IN             | IN         |  |  |

| 800     | IN             | IN         |  |  |

| 801     | OUT            | OUT        |  |  |

(2.3.3.4 TM990/303A FLOPPY CONTROLLER continued)

There are two types of errors reported by the system boot EPROMs. The first type comes directly from the 303A controller. These errors are reported as a single 16-bit 2's complement decimal integer by PDOS and a 4 digit hex number by the boot EPROMs. The error number is made up of the combined primary and secondary status words of the 303A command list. Since bit 1 is the error indicator, the absolute value of all 303A errors are always be greater than 16383. (Write protect error is intercepted and returned as error 103.)

TM990/303A disk controller errors are defined as follows:

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 0   | >8000 | OL = Off Line                |

| 1   | >4000 | ER = Error occurred          |

| 5   | >0400 | SI = Seek Incomplete         |

| 6   | >0200 | ST = Self Test Error         |

| 7   | >0100 | BC = Bad Command             |

| 9   | >0040 | DE = Data Error              |

| 11  | >0010 | ID = Disk ID Error           |

| 12  | >0008 | OV = Overrun Error           |

| 14  | >0002 | SE = Data Field Search Error |

| 15  | >0001 | UE = Unit Error              |

The second type of error is generated by the PDOS Device Service Routine. These errors include device time-out, device not installed, boundary errors, and errors resulting from incompatible data or media.

These errors are defined as follows:

- 68 = Attempt to write non-PDOS header.

- 100 = Device not installed.

- 101 = Sector too large.

- 102 = Device timeout.

- 103 = Write protect error.

- 109 = Attempt to read/write across 4k boundary.

- 110 = # of disk sides does not match data.

Track 0 is reserved for future use. For a standard disk, tracks 1 through 76 are available for data storage. This equals 1976 sectors or 1976 x 256 = 505,856 bytes per disk. (1,011,712 bytes for double sided disk.)

A boot disk restricts disk storage to tracks 1 through 71 or 1846 sectors (472,576 or 945,152 bytes/disk). Tracks 72 through 76 are reserved for the PDOS boot.

303A errors

### Primary status:

| <br> o1<br>' | <br>  El | <br>R¦I | <br>0 <br>'_ | <br> <br>_'_ | _•<br> si<br>_• | st | bc | •   | •  | <br>E <br>_' | •      | •   | •      | •     | •     | <br>JE  <br>' |

|--------------|----------|---------|--------------|--------------|-----------------|----|----|-----|----|--------------|--------|-----|--------|-------|-------|---------------|

| •            |          | ^       |              |              | ^               | ^  | ^  |     |    |              |        |     |        |       |       |               |

| 1            |          | 1       |              |              | !               | :  | 1  |     |    |              |        |     |        |       |       |               |

| •            |          |         |              |              | •               | •  | •  |     |    |              |        |     |        |       |       |               |

| 1            |          | 1       |              |              |                 | ł  | 1  |     | :  | Seco         | onda   | ary | sta    | atu   | IS:   |               |

| .^_          | •        | ^       | _•-          | <b>_·</b> _  | ^_              | ^_ | ^_ | . • | ·  | -·           |        | -·  | - •    |       |       | <b></b> •     |

| OL           | 1        | łW      | P¦           | 1            | SI              | ST | BC | 1   | ¦D | F¦DS         | 5   WF | H   | )   DP | RIN   | D¦S   | 50            |

| '            | '        | -'-     | -'-          | -'-          | -'              | ·  | •  | •   | •• | - '          | - '    | - ' | -'     | - ' - | - ' - | -'            |

| 0            | 1        | 2       | 3            | 4            | 5               | 6  | 7  | 8   | 9  | 10           | 11     | 12  | 13     | 14    | 15    | ;             |

| !            |          |         |              | !            |                 |    |    | !   |    |              |        | !   |        |       |       | !             |

Device Service Routine errors

Standard disk: 0 = Reserved 1-76 = PDOS file storage

Boot disk: 0 = Reserved 1-71 = PDOS file storage 72-76 = PDOS boot

### 2.3.4 SPECIAL PURPOSE

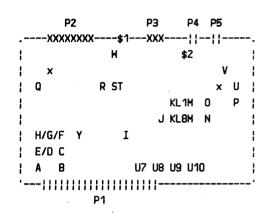

### 2.3.4.1 ER3318 GRAPHICS

\$2

SPEECH FREQUENCY

The ER3318 is a multi-purpose graphics board featuring two TMS9918 graphic processors, AM9511 arithmetic processor, ADC 0808 8 channel, 8 bit analog to digital converter, battery backed up clock, TMS5220 speech processor, 75469NA sound chip, and RAM/EPROM support.

Jumper configurations are defined as follows:

| A   | IN = INT8 ENABLE            | *OUT = INT8 DISABLE (SPEECH) |

|-----|-----------------------------|------------------------------|

| B   | IN = INT9 ENABLE            | *OUT = INT9 DISABLE (9511)   |

| C   | <b>*IN = READY.B ENABLE</b> | OUT = READY.B DISABLE        |

| D   | 1 = XA3 LOW                 | *2 = XA3 HIGH                |

| Ε   | *1 = XA2 LOW                | 2 = XA2 HIGH                 |

| F   | 1 = EXT ADR ENABLE          | *2 = EXT ADR DISABLE (101MA) |

| G   | *1 = XA1 LOW                | 2 = XA1 HIGH                 |

| н   | *1 = XAO LOW                | 2 = XAO HIGH                 |

| I   | 1 = 2532 4K EPROM           | *2 = 2516/4016 2K EPROM/RAM  |

| J   | 1 = 2532 4K EPROM           | *2 = 2516/4016 2K EPROM/RAM  |

| L1  | κ =                         | M =                          |

| L2  | K =                         | M =                          |

| L3  | κ =                         | M =                          |

| L4  | K =                         | M =                          |

| L5  | K =                         | H =                          |

| L6  | κ =                         | M =                          |

| L7  | κ =                         | M =                          |

| L8  | κ =                         | M =                          |

| Ν   | *1 = 4016 RAM               | 2 = 2516/2532 EPROM          |

| 0   | 1 = 2532 4K EPROM           | *2 = 2516/4016 2K EPROM/RAM  |

| Ρ   | *1 = 4116 16K VDP1 RAM      | 2 = 4027 4K VDP1 RAM         |

| Q   | 1 = 2 mhz 9511 CLOCK        | *2 = 3 mhz 9511 CLOCK        |

| R   | $1 = x_1xx$ ADDR BIAS       | *2 = >x3xx ADDR BIAS         |

| S   | 1 = >6xxx DECODE BASE       | *2 = >Exxx DECODE BASE       |

| T   | 1 = >6xxx DECODE BASE       | *2 = >Exxx DECODE BASE       |

| U   | *1 = 4116 16K VDP2 RAM      |                              |

| ۷   | *1 = VDP2 OVERLAY VDP1      | 2 = VDP2 OUT P5              |

| Η   | *1 = SPEECH AND SOUND       | 2 = SPEECH ONLY              |

| Υ.  | <b>*IN = NO WAIT STATE</b>  | OUT = WAIT STATE             |

| \$1 | Sound Volumn Control        |                              |

|     |                             |                              |

ER3318 MULTI-PURPOSE GRAPHICS BOARD:

ER3318 FUNCTIONAL LAYOUT:

| P2             | P3 P4     | 4 P5                                   |

|----------------|-----------|----------------------------------------|

| XXXXXXXXX      | \$XXX¦    |                                        |

| ; 0808-A/D     | amplifier | 1                                      |

| 5832-CLOCK     | SPEECH    | VDP2                                   |

| 1              | SOUND     | 1                                      |

| 1              |           | 1                                      |

| 9511-MATH      | decode    | VDP1 ;                                 |

| 1              |           | 1                                      |

| ¦ ready        | RAM/EPROM | 1                                      |

| interrupts     |           | 1                                      |

| '!!!!!!!!!!!!! |           | ······································ |

| P'             | 1         |                                        |

PAGE 2-30

### (2.3.4.1 ER3318 GRAPHICS continued)

| P2 | Pin #1 = | +5 VOLT | Pin #1 | 4 = | +5 VOL1 |     |       |

|----|----------|---------|--------|-----|---------|-----|-------|

|    | 2 =      | +5 VOLT | 1      | 5 = | GND     |     |       |

|    | 3 =      | +5 VOLT | 1      | 6 = | GND     |     |       |

|    | 4 =      | GND     | 1      | 7 = | CHANNEL | . 7 | INPUT |

|    | 5 =      | GND     | 1      | 8 = | CHANNEL | . 6 | INPUT |

|    | 6 =      | GND     | 1      | 9 = | CHANNEL | . 5 | INPUT |

|    | 7 =      | GND     | 2      | 0 = | CHANNEL | . 4 | INPUT |

|    | 8 =      | GND     | 2      | 1 = | CHANNEL | . З | INPUT |

|    | 9 =      | GND     | 2      | 2 = | CHANNEL | . 2 | INPUT |

|    | 10 =     | GND     | 2      | 3 = | CHANNEL | . 1 | INPUT |

|    | 11 =     | GND     | 2      | 4 = | CHANNEL | . 0 | INPUT |

|    | 12 =     | GND     | 2      | 5 = | GND     |     |       |

|    | 13 =     | GND     |        |     |         |     |       |

P3 Pin #1 = GND

- 2 = GND

- 3 = GND

- 4 = GND

- 5 = GND

- 6 = VIDEO OUT AUX

- 7 = VIDEO OUT MAIN

- 8 = EXTERNAL AUDIO AMP OUTPUT

- 9 = 8 OHM SPEAKER OUTPUT

### P4/P5 Pin #1 = GND

2 = Composite Video

3 = N/C

4 = +12 volts

### 2.3.4.2 TM990/302 EPROM PROGRAMMER

The TM990/302 is used for EPROM burning only in a PDOS system. The onboard RAM cannot be used and must be removed from the board. If problems still occur, the DBIN, WE, and READY signals should also be cut. The BURN302 utility is demonstrated below:

```

.BURN302

BURN302 R2.3e

*NOTE: ALL NUMBERS ARE HEX.

HIGHEST PC=0000

BUFFER LIMITS ARE 0000 TO 7072

0,<file>,<adr>

LOAD BINARY FILE

1, (file) {, (adr) }

LOAD OBJECT FILE

2, (adr1), (adr2), (byte) LOAD EPROM DATA

VERIFY BLANK EPROM

A

B{, <adr>}

SET BUFFER BASE

C, <adr1>, <adr2>, {<adr3>} COMPUTE CHECKSUM

Ε

EXIT TO PDOS

SET EPROM INDEX

I{,<adr>}

М

MODIFY BUFFER MEMORY

(adr1)

INSPECT

<adr1>,<adr2>

DISPLAY MEMORY

<adr1>,<adr2>,<adr3>

COPY MEMORY

0,<adr1>,<adr2>,<file>

OUTPUT OBJECT TO FILE

P, <adr1>, <adr2>, <byte> PROGRAM EPROM

S{,<step>}

SET STEP

SPECIFY EPROM TYPE

T{, <eprom>}

V, <adr1>, <adr2>, <byte> VERIFY EPROM WITH MEMORY

*8F000

HIGHEST PC=0000

BUFFER LIMITS ARE FOOD TO FFFF

*1,BOOT

ENTRY ADDRESS=0000

*PF000,FFFF,L

. . . . . . . . . . . . . .

VERIFYED!

*P,F000,FFFF,R

. . . . . . . . . . . . .

VERIFYED!

```

\*E

•

#### CHAPTER 2 INSTALLATION

#### 2.3.4.3 TM990/307 I/O EXTENDER

One or two TM990/307 cards may be used in conjunction with the TM990/101MA or TM990/102 CPU. A TM990/101MA CPU defines ports 3-6 on the first TM990/307 and ports 7 and 8 on the second. A TM990/102 would be the same if a TM990/303B with aux port is included. Otherwise, ports 2-5 would be on the first TM990/307 and ports 6-8 on the second. Any ports left over could be used for drivers, such as a modified \$TTA.

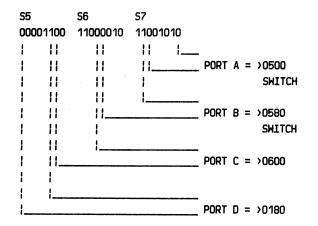

TM990/307 switches are set as follows:

- 1) Both TM990/307 cards are set for interrupt level 8. For the 1st TM990/307, switch packs S1 through S4 are set with switch 1 ON and switches 2-8 OFF. (See figure 2-2 of 307 manual.) For the 2nd TM990/307, switch packs S1, S2, and S3 have switch 1 ON and 2-8 OFF. Switch pack S4 has switches 1-8 OFF.

- The first TM990/307 board is set with CRU base addresses >0500, >0580, >0600, and >0180.

- 3) The second TM990/307 board, if used, is set with CRU base addresses of >0680, >0700, >0780, and >0800 (not used).

Optional PDOS 102 boot EPROMs which use DIP switches for auto-boot and device selection (SWFLG EQU 1) look to the first TM990/307 switch pack S8. These switches are defined as follows:

> SW8 OFF = AUTO BOOT SW7 OFF = TM990/303A (disks 0-3) SW6 OFF = ER3314 INSTALLED (disks 4-7) SW5 OFF = TM990/210 BUBBLE (disks 8-11)

Note #1: The 'sense' of these switches is opposite that found on the TM990/101M card. An 'OFF' (OPEN) indicates the feature is selected.

Note #2: In order for the TM990/102 to use the configuration switches on the first TM990/307 card, the CRU base addresses for ports A and B MUST be at >0500 and >0580 respectively. The system will not work if this is not correct.

TM990/307 RS232 EXPANSION CARD:

TM990/307 card #1 switch packs:

| S5       | S6       | S7             |

|----------|----------|----------------|

| 00001100 | 11000010 | 11001010       |

|          | 11       | II I           |

|          | 11       | Port A = >0500 |

|          | H        | ; SWITCH       |

|          | 11       | l              |

|          |          | PORT B = >0580 |

|          | 1        | SWITCH         |

| 1 11     | 1        |                |

|          |          | PORT C = >0600 |

|          |          |                |

|          |          |                |

| l        |          | PORT D = >0180 |

TM990/307 card #2 switch packs:

### 2.3.5 CARD CAGE

For DHA logic cards to work properly, the etch between lines 95 and 96 of the backplane on the card cage must be open. This is done by either cutting the etch or by removing a stake-pin jumper at the slot on TM990/5X0A card cages. Jumpers marked J5, J6, J7, and J8 correspond to jumpers to set up slots 1 to 4 respectively. These jumpers are located inside the chassis on the backplane adjacent to their respective slots.

The cutting of the trace or removal of the stake-pin jumper allows the DMA logic to work correctly by letting the GRANTIN-GRANTOUT lines control DMA priority.

CHAPTER 2 INSTALLATION

PAGE 2-34

#### 2.4 SYSGEN

Due to the device independent nature of PDOS, very little system customizing is required. The main changes from system to system involve the terminal type and secondary storage devices. The latter is completely a function of the boot EPROMs and is covered in Chapter 8.

Storage media preparation is covered in this section, as Hell as procedures for customizing PDOS and backing up diskettes.

### 2.4.1 DISK FORMATTING

Before PDOS can use a disk or diskette, the disk must have various control and timing marks written on it (formatted), as well as PDOS directory and sector data (initialized). Formatting a disk is device dependent while initializing is common to all secondary storage devices.

A disk is formatted by one of the 'FRMTxxx' utilities. Since formatting is physical device dependent, the correct format program must be used. The device specification is always a logical unit number with respect to the physical device. This may be the same as the PDOS disk number, but not necessarily.

Formatting a disk unit completely destroys any existing data. Care should be exercised when formatting new disks so that good data is not inadvertently destroyed. Some suggestions include:

- 1) Enable write protect whenever possible on good diskettes.

- 2) Open drive doors or spin down drives of those not intended for formatting if unsure.

- 3) Always maintain current backups of all programs and data.

Devices such as bubble memories or RAM storage devices do not require formatting.

Customize 1) terminal type 2) secondary storage devices

.FRMT303 TM990/303A STANDARD FLOPPY FORMAT R2.4 DEVICE LOGICAL UNIT=1 SIDES=1 TRACK=0,76 FORMAT LOGICAL UNIT 1, SECTORS 0 TO 76?Y SUCCESS!!

.FRMTW FORMAT WINCHESTER R2.4 DEVICE LOGICAL UNIT=2 TRACK=COMPLETE DISK INTERLEAVE=3 FORMAT LOGICAL UNIT 2?Y \*\*\* CAUTION: DO NOT ACCESS DISK WHILE FORMATTING \*\*\* PLEASE WAIT.....SUCCESS!!

### 2.4.2 DISK INITIALIZING

Before PDOS can work with a new disk, it must be initialized so that directory and sector information is available for the file management module. The INIT utility initializes a formatted disk.

Six parameters are required to properly initialize a disk. First, enter the disk device number. Since INIT uses the system read/write routines, the disk device number corresponds to a physical device through the boot EPROMs. Thus, this number may be different from the FRMTxxx logical unit.

Next, enter the number of diskette sides and density. These parameters are required in the header sector for some devices. For others, such as winchester units, these parameters are meaningless. The boot EPROMs are the only routines that use these parameters.

The number of possible directory entries on the new disk unit is next. For best usage of disk storage, this number should be a multiple of 8. Once the number of files has been set, it can not be expanded until the disk is again initialized.

The number of PDOS sectors is the fifth prompt. This number is device dependent but the INIT menu helps you in remembering some of the common device sizes. The number of sectors can be less than the total number available on a device if you desire to reserve storage for other purposes (such as storing a system boot on the disk).

Finally, you enter the disk name. This name can be up to 16 characters in length and appears at the beginning of a directory, assembly, or catalog listing. Other than identification, the name has no significance to PDOS.

Since the INIT utility also destroys all data on a disk unit (up to the number of sectors specified), you must verify all parameters before proceeding.

The INIT utility initializes a formatted disk by creating the header and bit map sectors from prompt information and bad sector information gathered by writing to all disk sectors. If a bad sector is encountered during the initialize process, it is deallocated (removed) from the bit map and an error message is reported. Only the header and bit map sectors are required to be good sectors.

.INIT PDOS DISK INITIALIZATION R2.4 DISK #=6 SIDES=1 DENSITY=D MAXIMUM DIRECTORY SIZE=128 TOTAL NUMBER OF SECTORS=1846 DISK NAME=BACKUP #004 INIT: DISK #6 SINGLE SIDED DOUBLE DENSITY **128 FILE DIRECTORY** 1846 PDOS SECTORS OK?Y PLEASE WAIT ..... SUCCESS!!

### CHAPTER 2 INSTALLATION

PAGE 2-36

### 2.4.3 CUSTOMIZING PDOS

The BFIX utility customizes a PDOS system for specific applications. To ensure a valid system, you should execute BFIX only after a system boot. Creating new tasks or executing BASIC may alter the PDOS initialization routines making reinitialization impossible.

The following areas of PDOS are customized with the BFIX utility:

- 1. PDOS and BASIC terminal control codes.

- 2. Event timers.

- 3. System clock rate.

- 4. Console CRU addresses.

- 5. System 9901 interrupt mask.

- 6. Auto-start flag.

- 7. Auto-start file name.

- 8. Upper memory limit.

- 9. PDOS prompt characters.

1. PDOS and BASIC terminal control codes.

PDOS requires a console terminal to be able to clear the screen and position the cursor. PDOS BASIC supports other optional commands such as cursor movement, clear screen modes, and screen protection.

BFIX prompts for a terminal type from a set of predefined terminal definitions. If a code other than 'U' or (carriage return) is selected, then both PDOS and BASIC are adjusted accordingly. Otherwise, a series of prompts are output showing current control codes and asking for any changes.